# Lecture Notes in Computer Science Edited by G. Goos, J. Hartmanis and J. van Leeuwen

2162

# Springer Berlin

Berlin Heidelberg New York Barcelona Hong Kong London Milan Paris Tokyo Çetin K. Koç David Naccache Christof Paar (Eds.)

# Cryptographic Hardware and Embedded Systems – CHES 2001

Third International Workshop Paris, France, May 14-16, 2001 Proceedings

#### Series Editors

Gerhard Goos, Karlsruhe University, Germany Juris Hartmanis, Cornell University, NY, USA Jan van Leeuwen, Utrecht University, The Netherlands

Volume Editors

Çetin K. Koç Oregon State University, ECE Department Corvallis, Oregon 97331, USA E-mail: Koc@ece.orst.edu

David Naccache

Gemplus Card International

34 rue Guynemer, 92447 Issy les Moulineaux Cedex, France

E-mail: David.Naccache@gemplus.com

Christof Paar Worcester Polytechnic Institute, ECE Department Worcester, MA 01609, USA E-mail: christof@ece.wpi.edu

Cataloging-in-Publication Data applied for

Die Deutsche Bibliothek - CIP-Einheitsaufnahme

Cryptographic hardware and embedded systems: third international workshop; proceedings / CHES 2001, Paris, France, May 14 - 16, 2001. Çetin K. Koç ... (ed.). - Berlin; Heidelberg; New York; Barcelona; Hong Kong; London; Milan; Paris; Tokyo: Springer, 2001 (Lecture notes in computer science; Vol. 2162) ISBN 3-540-42521-7

CR Subject Classification (1998): E.3, C.2, C.3, B.7.2, G.2.1, D.4.6, K.6.5, F.2.1, J.2

ISSN 0302-9743 ISBN 3-540-42521-7 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag Berlin Heidelberg New York a member of BertelsmannSpringer Science+Business Media GmbH

http://www.springer.de

© Springer-Verlag Berlin Heidelberg 2001 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Steingräber Satztechnik GmbH Printed on acid-free paper SPIN 10840313 06/3142 5 4 3 2 1 0

# **Preface**

These are the proceedings of CHES 2001, the third Workshop on Cryptographic Hardware and Embedded Systems. The first two CHES Workshops were held in Massachusetts, and this was the first Workshop to be held in Europe. There was a large number of submissions this year, and in response the technical program was extended to  $2\ 1/2$  days.

As is evident by the papers in these proceedings, many excellent submissions were made. Selecting the papers for this year's CHES was not an easy task, and we regret that we had to reject several very intersting papers due to the lack of time. There were 66 submitted contributions this year, of which 31, or 47%, were selected for presentation. If we look at the number of submitted papers at CHES '99 (42 papers) and CHES 2001 (51 papers), we observe a steady increase. We interpret this as a continuing need for a workshop series which combines theory and practice for integrating strong security features into modern communications and computer applications. In addition to the submitted contributions, Ross Anderson from Cambridge University, UK, and Adi Shamir from The Weizmann Institute, Israel, gave invited talks.

As in previous years, the focus of the workshop is on all aspects of cryptographic hardware and embedded system design. Of special interest were contributions that describe new methods for efficient hardware implementations and high-speed software for embedded systems, e.g., smart cards, microprocessors, DSPs, etc. CHES also continues to be an important forum for new theoretical and practical findings in the important and growing field of side-channel attacks.

We hope to continue to make the CHES workshop series a forum of intellectual exchange in creating secure, reliable, and robust security solutions of tomorrow. CHES Workshops will continue to deal with hardware and software implementations of security functions and systems, including security for embedded wireless ad-hoc networks.

We thank everyone whose involvement made the CHES Workshop such a successful event, in particular we would like to thank André Weimerskirch from WPI, and Delphine Abecassis and Cécile Osta from Novamedia for their efforts.

May 2001

Çetin K. Koç David Naccache Christof Paar

# Acknowledgements

The program chairs express their thanks to the program committee, the referees for their help in selecting the best quality papers, and also the companies which provided support to the workshop.

The program committee members of CHES 2001:

- Ross Anderson (Ross.Anderson@cl.cam.ac.uk)

University of Cambridge, U.K.

- Jean-Sebastien Coron (Jean-Sebastien.CORON@gemplus.com)

Gemplus. France

- Kris Gaj (kgaj@gmu.edu)

George Mason University, USA

- Jim Goodman JGoodman@chrysalis-its.com> Chrysalis-ITS, Canada

- Anwar Hasan (ahasan@arith1.vlsi.uwaterloo.ca) University of Waterloo, Canada

- Peter Kornerup (kornerup@imada.sdu.dk)

Odense University, Denmark

- Bart Preneel (Bart.Preneel@esat.kuleuven.ac.be)

Université Catholique de Louvain, Belgium

- Jean-Jacques Quisquater (jjq@dice.ucl.ac.be)

Université Catholique de Louvain, Belgium

- Patrice L. Roussel (proussel@ichips.intel.com) Intel Corporation, USA

- Christoph Ruland (RULAND@nue.et-inf.uni-siegen.de) Universität Siegen, Germany

- Erkay Savaş (erkay@rTrust.com)

rTrust, USA

- Joseph Silverman (jhs@ntru.com)

Brown University and NTRU Cryptosystems, Inc., USA

- Jacques Stern (Jacques.Stern@ens.fr) Ecole Normale Superieure, France

- Colin Walter (C.Walter@sna.co.umist.ac.uk)

Computation Department UMIST, U.K.

- Michael Wiener (michael.wiener@entrust.com)

Entrust Technologies, Canada

# The referees of CHES 2001:

- Tolga Acar (tacar@novell.com)

- Andre Adelsbach (anadel@cs.uni-sb.de)

- Ross Anderson (Ross.Anderson@cl.cam.ac.uk)

- Philippe Anguita (Philippe.Anguita@gemplus.com)

- Eric Brier (Eric.Brier@gemplus.com)

- Marco Bucci (Marco.Bucci@gemplus.com)

- Denis Carabin (Denis.Carabin@gemplus.com)

- Mahieu Ciet (ciet@dice.ucl.ac.be)

- Christophe Clavier (Christophe.Clavier@gemplus.com)

- Jean-Sebastien Coron (coron@clipper.ens.fr)

- Nora Dabbous (nora.dabbous@gemplus.com)

- Jean-Francois Dhem (Jean-Francois.Dhem@gemplus.com)

- Adam Elbirt (aelbirt@nac.net)

- Nathalie Feyt (Nathalie.Feyt@gemplus.com)

- Kris Gaj (kgaj@gmu.edu)

- Jovan Golic (Jovan.Golic@gemplus.com)

- Guang Gong (ggong@cacr.math.uwaterloo.ca)

- Jim Goodman (jimg@mtl.mit.edu)

- Jorge Guajardo (guajardo@ece.wpi.edu)

- Frank Gurkaynak (kgf@WPI.EDU)

- Helena Handschuh (Helena. Handschuh@gemplus.com)

- Anwar Hasan (ahasan@claude.uwaterloo.ca)

- Marc Joye (Marc.Joye@gemplus.com)

- Cetin Koc (koc@ece.orst.edu)

- Francois Koeune (koeune@dice.ucl.ac.be)

- Peter Kornerup (kornerup@imada.sdu.dk)

- Spyros Magliveras (spyros@cse.unl.edu)

- Bill Martin (martin@WPI.EDU)

- Renato Menicocci (Renato.Menicocci@gemplus.com)

- Tom Messerges (Tom\_Messerges-ADTL01@email.mot.com)

- Pascal Moitrel (Pascal.Moitrel@gemplus.com)

- Guglielmo Morgari (Guglielmo.MORGARI@gemplus.com)

- Christophe Mourtel (Christophe.Mourtel@gemplus.com)

- David Mraihi (David.Mraihi@gemplus.com)

- Gerardo Orlando (Gerardo.Orlando@GSC.GTE.Com)

- Christof Paar (christof@ece.wpi.edu)

- Marco Paggio (Marco.Paggio@gemplus.com)

- Pascal Paillier (Pascal.Paillier@gemplus.com)

- Bart Preneel (bart.preneel@esat.kuleuven.ac.be)

- Florence Ques (Florence.Ques@gemplus.com)

- Jean-Jacques Quisquater (jjq@dice.ucl.ac.be)

- Jean-Marc Robert (jean-marc.robert@gemplus.com)

- Francisco Rodriguez (rodrigfr@ece.orst.edu)

- Ludovic Rousseau (Ludovic.Rousseau@gemplus.com)

- Patrice Roussel (proussel@ichips.intel.com)

- Christoph Ruland (RULAND@nue.et-inf.uni-siegen.de)

- Erkay Savas (savas@ece.orst.edu)

- Tom Schmidt (toms@math.orst.edu)

- Joseph Silverman (jhs@ntru.com)

- Nigel Smart (nigel@cs.bris.ac.uk)

- Jacques Stern (jacques.stern@ens.fr)

- Berk Sunar (sunar@ece.wpi.edu)

- Alex Tenca (tenca@ece.orst.edu)

- van Trung Tran (trung@exp-math.uni-essen.de)

- Michael Tunstall (Michael.Tunstall@gemplus.com)

- Christophe Tymen (Christophe.Tymen@gemplus.com)

- Colin Walter (C.Walter@co.umist.ac.uk)

- Andre Weimerskirch (weika@ece.wpi.edu)

- Michael Wiener (michael.wiener@entrust.com)

- Ed Witzke (elwitzk@sandia.gov)

- Huapeng Wu (h3wu@cacr.math.uwaterloo.ca)

# The companies which provided support to CHES 2001:

- Gemplus http://www.gemplus.com

- NTRU Cryptosystems, Inc. http://www.ntru.com

- rTrust http://www.rtrust.com

- Secusys http://www.secusys.com

# Table of Contents

| Page                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------|

| Invited Talk                                                                                                      |

| Protecting Embedded Systems – The Next Ten Years                                                                  |

| Side Channel Attacks I                                                                                            |

| A Sound Method for Switching between Boolean and Arithmetic Masking $\dots 3$ $L.$ $Goubin$                       |

| Fast Primitives for Internal Data Scrambling in Tamper Resistant Hardware                                         |

| Random Register Renaming to Foil DPA                                                                              |

| Randomized Addition-Subtraction Chains as a Countermeasure against Power Attacks                                  |

| Rijndael Hardware Implementations                                                                                 |

| Architectural Optimization for a 1.82Gbits/sec VLSI Implementation of the AES Rijndael Algorithm                  |

| High Performance Single-Chip FPGA Rijndael Algorithm                                                              |

| Two Methods of Rijndael Implementation in Reconfigurable Hardware $\ldots.77$ $V.FischerandM.Drutarovsk\acute{y}$ |

| Random Number Generators                                                                                          |

| Pseudo-random Number Generation<br>on the IBM 4758 Secure Crypto Coprocessor                                      |

| Efficient Online Tests for True Random Number Generators                                                          |

| Elliptic Curve Algorithms                                                                                                                           |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| The Hessian Form of an Elliptic Curve                                                                                                               |  |  |

| Efficient Elliptic Curve Cryptosystems from a Scalar Multiplication Algorithm with Recovery of the y-Coordinate on a Montgomery-Form Elliptic Curve |  |  |

| Generating Elliptic Curves of Prime Order                                                                                                           |  |  |

| Invited Talk                                                                                                                                        |  |  |

| New Directions in Croptography                                                                                                                      |  |  |

| Arithmetic Architectures                                                                                                                            |  |  |

| A New Low Complexity Parallel Multiplier for a Class of Finite Fields $\dots$ 160 $M$ . Leone                                                       |  |  |

| Efficient Rijndael Encryption Implementation with Composite Field Arithmetic                                                                        |  |  |

| High-Radix Design of a Scalable Modular Multiplier                                                                                                  |  |  |

| A Bit-Serial Unified Multiplier Architecture for Finite Fields $\operatorname{GF}(p)$ and $\operatorname{GF}(2^m)$                                  |  |  |

| Cryptanalysis                                                                                                                                       |  |  |

| Attacks on Cryptoprocessor Transaction Sets                                                                                                         |  |  |

| Bandwidth-Optimal Kleptographic Attacks                                                                                                             |  |  |

| Electromagnetic Analysis: Concrete Results                                                                                                          |  |  |

| Embedded Implementations and New Ciphers                                                             |

|------------------------------------------------------------------------------------------------------|

| NTRU in Constrained Devices                                                                          |

| Transparent Harddisk Encryption                                                                      |

| Side Channel Attacks II                                                                              |

| Sliding Windows Succumbs to Big Mac Attack                                                           |

| Universal Exponentiation Algorithm: A First Step towards <i>Provable</i> SPA-Resistance              |

| An Implementation of DES and AES, Secure against Some Attacks 309 M. Akkar and C. Giraud             |

| Hardware Implementations of Ciphers                                                                  |

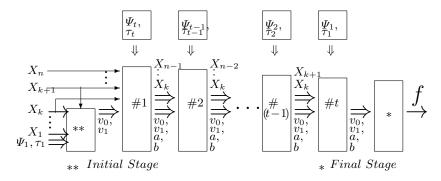

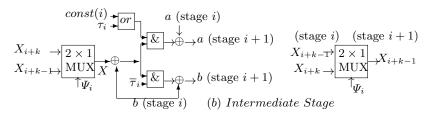

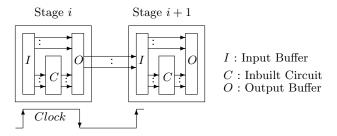

| Efficient Implementation of "Large" Stream Cipher Systems                                            |

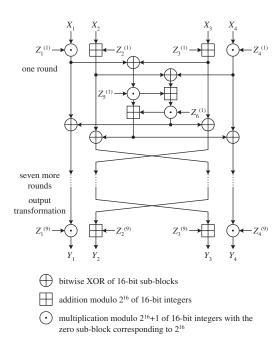

| Tradeoffs in Parallel and Serial Implementations of the International Data Encryption Algorithm IDEA |

| A Scalable $GF(p)$ Elliptic Curve Processor Architecture for Programmable Hardware                   |

| Implementation of RSA Algorithm  Based on RNS Montgomery Multiplication                              |

# Side Channel Attacks on Elliptic Curve Cryptosystems

| Protections against Differential Analysis for Elliptic Curve Cryptography: |    |

|----------------------------------------------------------------------------|----|

| An Algebraic Approach                                                      | 77 |

| M. Joye and C. Tymen                                                       |    |

| Preventing SPA/DPA in ECC Systems Using the Jacobi Form                    | 91 |

| Hessian Elliptic Curves and Side-Channel Attacks                           | ე2 |

| Author Index 41                                                            | 11 |

# Protecting Embedded Systems – The Next Ten Years

#### Ross Anderson

Computer Laboratory,

Pembroke Street, Cambridge, England

Ross.Anderson@cl.cam.ac.uk

**Abstract.** In this talk, I will speculate about the likely near-term and medium-term scientific developments in the protection of embedded systems.

A common view of the Internet divides its history into three waves, the first being centered around mainframes and terminals, and the second (from about 1992 until now) on PCs, browsers, and a GUI. The third wave, starting now, will see the connection of all sorts of devices that are currently in proprietary networks, standalone, or even non-computerized. By the end of 2003, there might well be more mobile phones connected to the Internet than computers. Within a few years we will see many of the world's fridges, heart monitors, bus ticket dispensers, burglar alarms, and electricity meters talking IP. By 2010, 'ubiquitous computing' will be part of our lives.

Some of the likely effects of ubiquitous computing are already apparent. For example, applications with intermittent connectivity will have to maintain much of their security state locally rather than globally. This will create new markets for processors with appropriate levels of tamper-resistance. But what will this mean?

I will discuss protection requirements at four levels.

Invasive attacks on hardware are likely to remain possible for capable motivated opponents, at least for devices that cannot be furnished with effective tamper responding barriers. That said, even commodity smartcards are much harder to probe than was the case five years ago. Decreasing feature sizes, 32-bit processors, and layout that makes bus lines harder to find and to probe, all combine to push up the entry cost. Attacks that could be done in a few weeks with ten thousand dollars' worth of equipment now take months and require access to equipment costing several hundred thousand dollars. However, this field rides on the coat-tails of the semiconductor test industry, and will remain unpredictable. Every so often, bright ideas lead to powerful new low-cost testing tools, that may be used in attacks. The scanning capacitance microscope may be one such.

Non-invasive attacks on hardware – such as power and glitch attacks – might become infeasible against even the smallest processors. However, this is not as easy as it seemed three or four years ago. Current techniques, such as randomised clocking, can only do so much. New ideas are needed, and I will discuss an EU-funded

research project (G3Card) to develop these. Its goal is produce a prototype smartcard CPU that is inherently resistant to noninvasive attacks. The prototypes currently being designed at Cambridge under G3Card use asynchronous (self-timed) dual-rail logic, which holds out the prospect of power consumption that is independent of the data being processed. This technology holds out the prospect of important side benefits as well, such as reduced RFI/EMI and lower power consumption.

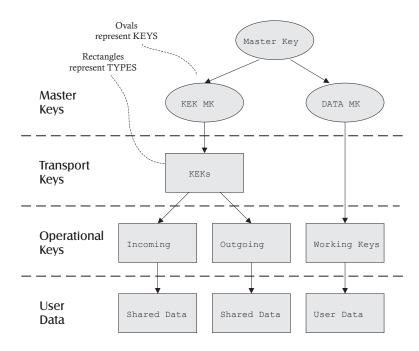

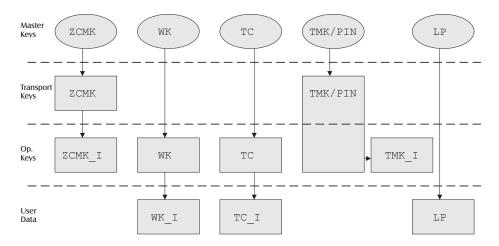

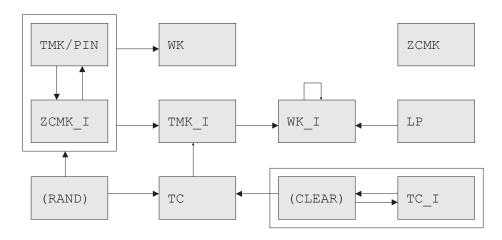

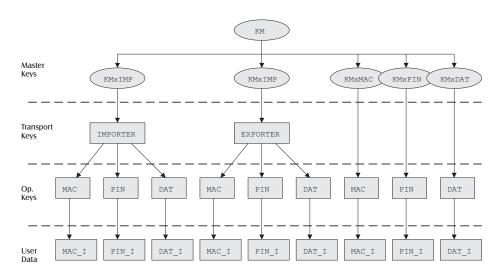

Protocol-level attacks continue to be a terrible problem. The design of ordinary authentication protocols is well known to be hard; yet a typical cryptographic processor performs much more than one protocol. Its API may have to support somewhere between a few dozen and a few hundred different cryptographic transactions. The paper in these proceedings by Mike Bond shows that attacks can be found on even the most mature and thoroughly-studied cryptographic APIs. Developing the tools and concepts to design robust cryptographic APIs looks set to be a major research challenge for some years to come, and may be the next big topic for the protocol research community.

Business process failures are coming to be recognised as perhaps the main cause of attacks on real systems. Once the principal providing the protection is no longer the same as the principal who will suffer loss if it fails, things become messy. While a traditional monolithic pay-TV operator might have owned the smartcard designer, the satellite transponder, the set-top boxes and indeed the entire customer base, things are now becoming much more fragmented. Design, evaluation, implementation and operations are being ever more widely distributed, and this is starting to introduce serious evaluation and assurance issues. There are also economic issues such as network externalities, asymmetric information, moral hazard, adverse selection, liability dumping and the tragedy of the commons.

The above themes interact in unexpected ways. For example, even a completely tamper-proof chip can have its design read out by a litigation attack; the attacker buys a vaguely relevant patent, brings a lawsuit against the device designer for infringement, and obtains full design details as part of the legal discovery process. This may be a further argument in favour of Kerckhoffs' principle. On the other hand, a highly obscure design can greatly complicate matters for an attacker whose tools allow him to observe only partial information about the computations being undertaken.

Ultimately, though, information security is about power. While at the technical level it is about controlling who may use which resource and how, while at the level of business strategy it is increasingly about raising barriers to trade, segmenting markets and differentiating products. A final point is that sometimes insecurity is welcome. For example, it may foster economic growth by making monopolies harder to defend.

# A Sound Method for Switching between Boolean and Arithmetic Masking

#### Louis Goubin

Schlumberger - CP8

68 route de Versailles, F-78431 Louveciennes, France

Louis.Goubin@louveciennes.tt.slb.com

**Abstract.** Since the announcement of the Differential Power Analysis (DPA) by Paul Kocher and al., several countermeasures were proposed in order to protect software implementations of cryptographic algorithms. In an attempt to reduce the resulting memory and execution time overhead, a general method was recently proposed, consisting in "masking" all the intermediate data.

This masking strategy is possible if all the fundamental operations used in a given algorithm can be rewritten with masked input data, giving masked output data. This is easily seen to be the case in classical algorithms such as DES or RSA.

However, for algorithms that combine boolean and arithmetic functions, such as IDEA or several of the AES candidates, two different kinds of masking have to be used. There is thus a need for a method to convert back and forth between boolean masking and arithmetic masking.

A first solution to this problem was proposed by Thomas Messerges in [15], but was unfortunately shown (see [6]) insufficient to prevent DPA. In the present paper, we present two new practical algorithms for the conversion, that are proven secure against DPA.

The first one ("BooleanToArithmetic") uses a constant number of elementary operations, namely 7, on the registers of the processor. The number of elementary operations for the second one ("ArithmeticToBoolean"), namely 5K+5, is proportional to the size K (in bits) of the processor registers.

**Key words:** Physical attacks, Differential Power Analysis, Electric consumption, AES, IDEA, Smartcards, Masking Techniques.

### 1 Introduction

Paul Kocher and al. introduced in 1998 ([12]) and published in 1999 ([13]) the concept of *Differential Power Analysis* attack, also known as DPA. The initial focus was on symmetrical cryptosystems such as DES (see [12,16]) and the AES candidates (see [1,3,7]), but public key cryptosystems have since been shown to be also vulnerable to the DPA attacks (see [17,5,11]).

In [10,11], Goubin and Patarin proposed a generic countermeasure consisting in splitting all the intermediate variables. A similar "duplication" method

was suggested shortly after by Chari and al. in [3] and [4]. Although the authors of [3] state that these general methods generally increase dramatically the amount of memory needed, or the computation time, Goubin and Patarin proved that realistic implementations could be reached with the "duplication" method. However, it has been shown in [9] that even inner rounds can be aimed by "Power-Analysis"-type attacks, so that the splitting should be performed on all rounds of the algorithm. This makes the issue of the memory and time computation overhead even more crucial, especially for embedded systems such as smartcards.

In [15], Thomas Messerges investigated on DPA attacks applied on the AES candidates. He developed a general countermeasure, consisting in masking all the inputs and outputs of each elementary operation used by the microprocessor. This generic technique allowed him to evaluate the impact of these countermeasures on the five AES algorithms.

However, for algorithms that combine boolean and arithmetic functions, two different kinds of masking have to be used. There is thus a need for a method to convert back and forth between boolean masking and arithmetic masking. This is typically the case for IDEA [14] and for three AES candidates: MARS [2], RC6 [18] and Twofish [19].

T. Messerges proposed in [15] an algorithm in order to perform this conversion between a "⊕ mask" and a "+ mask". Unfortunately, Coron and Goubin described in [6] a specific attack, showing that the "BooleanToArithmetic" algorithm proposed by T. Messerges is not sufficient to prevent Differential Power Analysis. In a similar way, his "ArithmeticToBoolean" algorithm is not secure either.

In the present paper, we present two new "BooleanToArithmetic" and "ArithmeticToBoolean" algorithms, proven secure against DPA attacks. Each of these algorithms uses only very simple operations: "XOR", "AND", subtractions and "logical shift left". Our "BooleanToArithmetic" algorithm uses a constant number (namely 7) of such elementary operations, whereas the number of elementary operations involved in our "ArithmeticToBoolean" algorithm is proportional (namely equal to 5K+5) to the size (i.e. the number K of bits) of the processor registers.

# 2 Background

# 2.1 The "Differential Power Analysis" Attack

The "Differential Power Analysis" (DPA) is an attack that allows to obtain information about the secret key (contained in a smartcard for example), by performing a statistical analysis of the electric consumption records measured for a large number of computations with the same key.

This attack does not require any knowledge about the individual electric consumption of each instruction, nor about the position in time of each of these instructions. It applies exactly the same way as soon as the attacker knows the

outputs of the algorithm and the corresponding consumption curves. It only relies on the following fundamental hypothesis:

Fundamental hypothesis: There exists an intermediate variable, that appears during the computation of the algorithm, such that knowing a few key bits (in practice less than 32 bits) allows us to decide whether two inputs (respectively two outputs) give or not the same value for this variable.

# 2.2 The Masking Method

In the present paper, we focus on the "masking method", initially suggested by Goubin and Patarin in [10], and studied further in [11].

The basic principle consists in programming the algorithm so that the fundamental hypothesis above is not true any longer (i.e. an intermediate variable never depends on the knowledge of an easily accessible subset of the secret key). More precisely, using a secret sharing scheme, each intermediate variable that appears in the cryptographic algorithm is splitted. Therefore, an attacker has to analyze multiple point distributions, which makes his task grow exponentially in the number of elements in the splitting.

#### 2.3 The Conversion Problem

For algorithms that combine boolean and arithmetic functions, two different kinds of masking have to be used:

Boolean masking:  $x' = x \oplus r$ Arithmetic masking:  $A = x - r \mod 2^K$

Here the variable x is masked with random r to give the masked value x' (or A). Our goal is to find an efficient algorithm for converting from boolean masking to arithmetic masking and conversely, in which all intermediate variables are decorrelated from the data to be masked, so that it is secure against DPA.

In all the present paper, we suppose that the processor has K-bit registers (in practice, K is most of the time equal to 8, 16, 32 or 64). All the arithmetic operations (such as the addition "+", the subtraction "-", or the doubling "z + -2z") are considered modulo  $2^K$ . For simplicity, the "mod $2^K$ " will often be omitted in the sequel.

# 3 From Boolean to Arithmetic Masking

# 3.1 A Useful Algebraic Property

Let  $I = \{0, 1, 2, \dots, 2^K - 1\}$ , with  $K \ge 1$  being an integer. Let  $x' \in I$ . We consider the function  $\Phi_{x'}: I \to I$ , defined by:

$$\Phi_{x'}(r) \equiv (x' \oplus r) - r \bmod 2^K.$$

We identify each element of I with the sequence of coefficients in its binary representation, so that I can be viewed as a vector space of dimension K over GF(2), isomorphic to  $GF(2)^K$ .

#### Theorem 1

$$\varPhi_{x'}(r) = x' \oplus \bigoplus_{i=1}^{K-1} \left[ \left( \bigwedge_{j=1}^{i-1} \left( 2^j \overline{x'} \right) \right) \wedge \left( 2^i x' \right) \wedge \left( 2^i r \right) \right],$$

where  $\overline{x'}$  stands for the ones complement of x', and  $\wedge$  stands for the boolean "AND" operator.

See Appendix 1 for a proof of Theorem 1.

Corollary 1.1 The function  $\Phi_{x'}$  is affine over GF(2).

This result is an easy consequence of Theorem 1.

# 3.2 The "BooleanToArithmetic" Algorithm

Since  $\Phi_{x'}$  is affine over GF(2), the function  $\Psi_{x'} = \Phi_{x'} \oplus \Phi_{x'}(0)$  is linear over GF(2). Therefore, for any value  $\gamma$ ,

$$\Psi_{x'}(r) = \Psi_{x'}(\gamma \oplus (r \oplus \gamma)) = \Psi_{x'}(\gamma) \oplus \Psi_{x'}(r \oplus \gamma).$$

**Corollary 1.2** For any value  $\gamma$ , if we denote  $A = (x' \oplus r) - r$ , we also have

$$A = [(x' \oplus \gamma) - \gamma] \oplus x' \oplus [(x' \oplus (r \oplus \gamma)) - (r \oplus \gamma)].$$

$A = (x' \oplus r) - r$  can thus be obtained from the following algorithm:

# Algorithm 1. BooleanToArithmetic

**Require:** (x',r) such that  $x = x' \oplus r$ **Ensure:** (A,r) such that x = A + r

Initialize  $\varGamma$  to a random value  $\gamma$

$T \Leftarrow x' \oplus \Gamma$

$T \Leftarrow T - \varGamma$

$T \Leftarrow T \oplus x'$

$\varGamma \Leftarrow \varGamma \oplus r$

$A \Leftarrow x' \oplus \Gamma$

$A \Leftarrow A - \Gamma$

$A \Leftarrow A \oplus T$

The "BooleanToArithmetic" algorithm uses 2 auxiliary variables (T and  $\Gamma$ ), 1 random generation and 7 elementary operations (more precisely: 5 "XOR" and 2 subtractions).

# 3.3 Proof of Security against DPA

From the description of the "BooleanToArithmetic" algorithm, we easily obtain the list of all the intermediate values  $V_0$ , ...,  $V_6$  that appear during the computation of  $A = (x' \oplus r) - r$ :

$$\begin{cases} V_0 = \gamma \\ V_1 = \gamma \oplus r \\ V_2 = x' \oplus \gamma \\ V_3 = (x' \oplus \gamma) - \gamma \\ V_4 = [(x' \oplus \gamma) - \gamma] \oplus x' \\ V_5 = x' \oplus \gamma \oplus r \\ V_6 = (x' \oplus \gamma \oplus r) - (\gamma \oplus r) \end{cases}$$

$$\gamma \text{ is randomly chosen with a}$$

If we suppose that  $\gamma$  is randomly chosen with a uniform distribution on  $I = \{0, 1\}^K$ , it is easy to see that:

- the values  $V_0$ ,  $V_1$ ,  $V_2$  and  $V_5$  are uniformly distributed on I.

- the distributions of  $V_3$ ,  $V_4$  and  $V_6$  depend on x' but not on r.

# 4 From Arithmetic to Boolean Masking

# 4.1 A Useful Recursion Formula

**Theorem 2** If we denote  $x' = (A + r) \oplus r$ , we also have  $x' = A \oplus u_{K-1}$ , where  $u_{K-1}$  is obtained from the following recursion formula:

$$\begin{cases} u_0 = 0 \\ \forall k \ge 0, \ u_{k+1} = 2[u_k \wedge (A \oplus r) \oplus (A \wedge r)]. \end{cases}$$

See Appendix 2 for a proof of Theorem 2.

# 4.2 The "ArithmeticToBoolean" Algorithm

Let  $\gamma$  be any value. The change of variable  $t_k = 2\gamma \oplus u_k$  leads to the following consequence of Theorem 2.

**Corollary 2.1** For any value  $\gamma$ , if we denote  $x' = (A + r) \oplus r$ , we also have  $x' = A \oplus 2\gamma \oplus t_{K-1}$ , where  $t_{K-1}$  is obtained from the following recursion formula:

$$\begin{cases} t_0 = 2\gamma \\ \forall k \geq 0, \ t_{k+1} = 2[t_k \wedge (A \oplus r) \oplus \omega], \end{cases}$$

in which  $\omega = \gamma \oplus (2\gamma) \wedge (A \oplus r) \oplus A \wedge r$ .

As a consequence,  $x'=(A+r)\oplus r$  can be obtained from the "Arithmetic-ToBoolean" algorithm below.

This method requires 3 auxiliary variables  $(T, \Omega \text{ and } \Gamma)$ , 1 random generation and (5K+5) elementary operations (more precisely: (2K+4) "XOR", (2K+1) "AND" and K "logical shift left").

# Algorithm 2. ArithmeticToBoolean

```

Require: (A, r) such that x = A + r

Ensure: (x',r) such that x=x'\oplus r

Initialize \Gamma to a random value \gamma

T \Leftarrow 2\Gamma

x' \Leftarrow \Gamma \oplus r

\Omega \Leftarrow \Gamma \wedge x'

x' \Leftarrow T \oplus A

\Gamma \Leftarrow \Gamma \oplus x'

\Gamma \Leftarrow \Gamma \land r

\Omega \Leftarrow \Omega \oplus \Gamma

\Gamma \Leftarrow T \wedge A

\Omega \Leftarrow \Omega \oplus \Gamma

for k = 1 to K - 1 do

\Gamma \Leftarrow T \wedge r

\Gamma \Leftarrow \Gamma \oplus \Omega

T \Leftarrow T \wedge A

\Gamma \Leftarrow \Gamma \oplus T

T \Leftarrow 2\Gamma

end for

x' \Leftarrow x' \oplus T

```

# 4.3 Proof of Security against DPA

From the description of the "BooleanToArithmetic" algorithm, we easily obtain the list of all the intermediate values  $W_0$ , ...,  $W_{5K+4}$  that appear during the computation of  $x' = (A+r) \oplus r$ :

```

\begin{cases} W_0 = \gamma \\ W_1 = 2\gamma \\ W_2 = \gamma \oplus r \\ W_3 = \gamma \oplus \gamma \wedge r \\ W_4 = 2\gamma \oplus A \\ W_5 = \gamma \oplus 2\gamma \oplus A \\ W_6 = (\gamma \oplus 2\gamma \oplus A) \wedge r \\ W_7 = \gamma \oplus (2\gamma) \wedge r \oplus A \wedge r \\ W_8 = (2\gamma) \wedge A \\ W_9 = \gamma \oplus (2\gamma) \wedge (A \oplus r) \oplus A \wedge r = \omega \\ \begin{cases} W_{5k+5} = (2\gamma \oplus u_{k-1}) \wedge r \\ W_{5k+6} = \gamma \oplus (2\gamma) \wedge A \oplus u_{k-1} \wedge r \oplus A \wedge r \\ W_{5k+7} = (2\gamma \oplus u_{k-1}) \wedge A \\ W_{5k+8} = \gamma \oplus u_{k-1} \wedge (A \oplus r) \oplus A \wedge r \\ W_{5k+9} = 2\gamma \oplus u_k \end{cases}

```

If we suppose that  $\gamma$  is randomly chosen with a uniform distribution on  $I = \{0, 1\}^K$ , it is easy to see that:

- the values  $W_0$ ,  $W_2$  and  $W_{5k+8}$   $(1 \le k \le K-1)$  are uniformly distributed on I.

- the values  $W_1$  and  $W_{5k+9}$  are uniformly distributed on the subset  $\{0,1\}^{K-1} \times \{0\}$  of I.

- the distributions of  $W_3$  and  $W_{5k+5}$   $(1 \le k \le K-1)$  depend on r but not on A.

- the distributions of  $W_4$ ,  $W_8$  and  $W_{5k+7}$   $(1 \le k \le K-1)$  depend on A but not on r.

To study the distribution of the remaining values  $(W_5, W_6, W_7, W_9)$  and  $W_{5k+6}$ , we will make use of the following result:

**Theorem 3** For any  $\delta \in I$ , the following function is bijective:

$$\Theta_{\delta}: \left\{ \begin{matrix} I \to I \\ \gamma \vdash \xrightarrow{\gamma} \oplus (2\gamma) \land \delta. \end{matrix} \right.$$

See Appendix 3 for a proof of Theorem 3. As a result:

- the values  $W_5 = \Theta_{-1}(\gamma) \oplus A$ ,  $W_7 = \Theta_r(\gamma) \oplus A \wedge r$ ,  $W_9 = \Theta_{A \oplus r}(\gamma) \oplus A \wedge r$  and  $W_{5k+6} = \Theta_r(\gamma) \oplus u_{k-1} \wedge r \oplus A \wedge r$  ( $1 \le k \le K-1$ ) are uniformly distributed on I.

- the distribution of  $W_6 = (\Theta_{-1}(\gamma) \oplus A) \wedge r$  depends on r but not on A.

# 5 Conclusion

In this paper, we solved the following open problem (stated in [6]): "find an efficient algorithm for converting from boolean masking to arithmetic masking and conversely, in which all intermediate variables are decorrelated from the data to be masked, so that it is secure against DPA".

The construction of our "BooleanToArithmetic" and "ArithmeticToBoolean" algorithms also led us to prove some results of independent interest. In particular we proved that  $r \vdash \neg (a \oplus r) - r \mod 2^K$  is an affine function, which seems to be a new result.

Finally, a direction for further research would be to find an improved version of the "ArithmeticToBoolean" algorithm, in which the number of elementary operations is less than 5K + 5, or (even better) a constant independent of the size K of the registers.

# Acknowledgement

I would like to thank Jean-Sébastien Coron for interesting discussions and suggestions.

# References

- 1. Eli Biham and Adi Shamir, "Power Analysis of the Key Scheduling of the AES Candidates", in *Proceedings of the Second Advanced Encryption Standard (AES) Candidate Conference*,

- http://csrc.nist.gov/encryption/aes/round1/Conf2/aes2conf.htm, March 1999.

- Carolynn Burwick, Don Coppersmith, Edward D'Avignon, Rosario Gennaro, Shai Halevi, Charanjit Jutla, Stephen M. Matyas, Luke O'Connor, Mohammad Peyravian, David Safford and Nevenko Zunic, "MARS - A Candidate Cipher for AES", NIST AES Proposal, June 1998. Available at: http://www.research.ibm.com/security/mars.pdf

- Suresh Chari, Charantjit S. Jutla, Josyula R. Rao and Pankaj Rohatgi, "A Cautionary Note Regarding Evaluation of AES Candidates on Smart-Cards", in Proceedings of the Second Advanced Encryption Standard (AES) Candidate Conference, http://csrc.nist.gov/encryption/aes/round1/Conf2/aes2conf.htm, March 1999.

- Suresh Chari, Charantjit S. Jutla, Josyula R. Rao and Pankaj Rohatgi, "Towards Sound Approaches to Counteract Power-Analysis Attacks", in *Proceedings of Advances in Cryptology - CRYPTO'99*, Springer-Verlag, 1999, pp. 398-412.

- Jean-Sébastien Coron, "Resistance Against Differential Power Analysis for Elliptic Curve Cryptosystems", in Proceedings of Workshop on Cryptographic Hardware and Embedded Systems, Springer-Verlag, August 1999, pp. 292-302.

- Jean-Sébastien Coron and Louis Goubin, "On Boolean and Arithmetic Masking against Differential Power Analysis", in Proceedings of Workshop on Cryptographic Hardware and Embedded Systems, Springer-Verlag, August 2000.

- John Daemen and Vincent Rijmen, "Resistance Against Implementation Attacks:

A Comparative Study of the AES Proposals", in Proceedings of the Second Advanced Encryption Standard (AES) Candidate Conference,

http://csrc.nist.gov/encryption/aes/round1/Conf2/aes2conf.htm, March 1999.

- John Daemen, Michael Peters and Gilles Van Assche, "Bitslice Ciphers and Power Analysis Attacks", in Proceedings of Fast Software Encryption Workshop 2000, Springer-Verlag, April 2000.

- 9. Paul N. Fahn and Peter K. Pearson, "IPA: A New Class of Power Attacks", in Proceedings of Workshop on Cryptographic Hardware and Embedded Systems, Springer-Verlag, August 1999, pp. 173-186.

- 10. Louis Goubin and J. Patarin, "Procédé de sécurisation d'un ensemble électronique de cryptographie à clé secrète contre les attaques par analyse physique", European Patent, Schlumberger, February 4th, 1999, Publication Number: 2789535.

- 11. Louis Goubin and Jacques Patarin, "DES and Differential Power Analysis The Duplication Method", in *Proceedings of Workshop on Cryptographic Hardware and Embedded Systems*, Springer-Verlag, August 1999, pp. 158-172.

- Paul Kocher, Joshua Jaffe and Benjamin Jun, "Introduction to Differential Power Analysis and Related Attacks", http://www.cryptography.com/dpa/technical, 1998.

- Paul Kocher, Joshua Jaffe and Benjamin Jun, "Differential Power Analysis", in Proceedings of Advances in Cryptology – CRYPTO'99, Springer-Verlag, 1999, pp. 388-397.

- Xuejia Lai and James Massey, "A Proposal for a New Block Encryption Standard", in Advances in Cryptology - EUROCRYPT '90 Proceedings, Springer-Verlag, 1991, pp. 389-404.

- Thomas S. Messerges, "Securing the AES Finalists Against Power Analysis Attacks", in Proceedings of Fast Software Encryption Workshop 2000, Springer-Verlag, April 2000.

- Thomas S. Messerges, Ezzy A. Dabbish and Robert H. Sloan, "Investigations of Power Analysis Attacks on Smartcards", in *Proceedings of USENIX Workshop on Smartcard Technology*, May 1999, pp. 151-161.

- 17. Thomas S. Messerges, Ezzy A. Dabbish and Robert H. Sloan, "Power Analysis Attacks of Modular Exponentiation in Smartcards", in *Proceedings of Workshop on Cryptographic Hardware and Embedded Systems*, Springer-Verlag, August 1999, pp. 144-157.

- Ronald L. Rivest, Matthew J.B. Robshaw, Ray Sidney and Yiqun L. Yin, "The RC6 Block Cipher", v1.1, August 20, 1998. Available at: ftp://ftp.rsasecurity.com/pub/rsalabs/aes/rc6v11.pdf

- Bruce Schneier, John Kelsey, Doug Whiting, David Wagner, Chris Hall and Niels Ferguson, "Twofish: A 128-Bit Block Cipher", June 15, 1998, AES submission available at: http://www.counterpane.com/twofish.pdf

# Annex 1: Proof of Theorem 1

To prove theorem 1, we prove the following more precise result:

**Lemma 1** For any integer  $k \ge 1$ :

$$\Phi_{a}(r) \equiv \left\{ a \oplus \bigoplus_{i=1}^{k-1} \left[ \left( \bigwedge_{j=1}^{i-1} \left( 2^{j} \bar{a} \right) \right) \wedge \left( 2^{i} a \right) \wedge \left( 2^{i} r \right) \right] \right\}$$

$$-\Big[\Big(\bigwedge_{j=1}^{k-1} \left(2^j \bar{a}\right)\Big) \wedge \left(2^k a\right) \wedge \left(2^k r\right)\Big] \bmod 2^K,$$

where  $\bar{a}$  stands for the ones complement of a, and  $\wedge$  stands for the boolean "AND" operator.

Theorem 1 easily follows from Lemma 1, by considering the particular value k = K (and taking a = x').

To prove Lemma 1, we will use the following elementary result.

**Lemma 2** For any integers u and v:

$$u - v \equiv (u \oplus v) - 2(\bar{u} \wedge v) \bmod 2^K$$

.

Proof of Lemma 2 (sketch):  $u \oplus v$  gives almost the same result as u-v, except that carries have been forgotten. For a given index, a carry appears if and only if a '1' bit (from v) is subtracted from a '0' bit (from u), which corresponds to a '1' bit in  $\bar{u} \wedge v = 1$ . Since the carry is then subtracted in the next index,  $\bar{u} \wedge v$  has to be shifted left, which is the same as to be doubled, before being subtracted from  $u \oplus v$ .

Proof of Lemma 1: We proceed by induction on k.

- We first apply Lemma 2 with  $u = a \oplus r$  and v = r:

$$\Phi_a(r) \equiv (a \oplus r) - r \equiv a - 2(\overline{a \oplus r} \wedge r) \bmod 2^K.$$

Since  $\overline{a \oplus r} = a \oplus \overline{r}$ , we have:

$$\Phi_a(r) \equiv a - 2((a \oplus \bar{r}) \wedge r) \equiv a - 2(a \wedge r) \bmod 2^K$$

which proves the case k=1 of Lemma 1 (conventionally, the empty product  $\bigwedge_{i=1}^{0}$  equals the identity element of the  $\wedge$  operator).

- Let us suppose that the result of Lemma 1 is true for k:

$$\begin{split} \varPhi_a(r) &\equiv \left\{ a \oplus \bigoplus_{i=1}^{k-1} \left[ \left( \bigwedge_{j=1}^{i-1} \left( 2^j \bar{a} \right) \right) \wedge \left( 2^i a \right) \wedge \left( 2^i r \right) \right] \right\} \\ &- \left[ \left( \bigwedge_{i=1}^{k-1} \left( 2^j \bar{a} \right) \right) \wedge \left( 2^k a \right) \wedge \left( 2^k r \right) \right] \bmod 2^K \end{split}$$

and let us show that it is also true for k + 1.

Let

$$u = a \oplus \bigoplus_{i=1}^{k-1} \left[ \left( \bigwedge_{j=1}^{i-1} \left( 2^j \bar{a} \right) \right) \wedge \left( 2^i a \right) \wedge \left( 2^i r \right) \right]$$

and

$$v = \left(\bigwedge_{j=1}^{k-1} (2^j \bar{a})\right) \wedge (2^k a) \wedge (2^k r).$$

We first obtain:

$$u \oplus v = a \oplus \bigoplus_{i=1}^{k} \left[ \left( \bigwedge_{j=1}^{i-1} (2^{j} \bar{a}) \right) \wedge (2^{i} a) \wedge (2^{i} r) \right].$$

Moreover,

$$\bar{u} = \overline{a \oplus \bigoplus_{i=1}^{k-1} \left[ \left( \bigwedge_{j=1}^{i-1} \left( 2^{j} \bar{a} \right) \right) \wedge \left( 2^{i} a \right) \wedge \left( 2^{i} r \right) \right]}$$

$$= \bar{a} \oplus \bigoplus_{i=1}^{k-1} \left[ \left( \bigwedge_{j=1}^{i-1} \left( 2^{j} \bar{a} \right) \right) \wedge \left( 2^{i} a \right) \wedge \left( 2^{i} r \right) \right],$$

so that:

$$\bar{u} \wedge v = \left\{ \bar{a} \oplus \bigoplus_{i=1}^{k-1} \left[ \left( \bigwedge_{i=1}^{i-1} \left( 2^j \bar{a} \right) \right) \wedge \left( 2^i a \right) \wedge \left( 2^i r \right) \right] \right\}$$

$$\wedge \Big(\bigwedge_{j=1}^{k-1} \left(2^j \bar{a}\right)\Big) \wedge \left(2^k a\right) \wedge \left(2^k r\right).$$

Therefore

$$\bar{u} \wedge v = \left(\bigwedge_{j=0}^{k-1} \left(2^j \bar{a}\right)\right) \wedge \left(2^k a\right) \wedge \left(2^k r\right)$$

because to each index  $i, 1 \le i \le k-1$  in u corresponds an index  $j, 1 \le j \le k-1$  in v (namely j=i), such that:

$$(2^i a) \wedge (2^j \bar{a}) = 0.$$

Therefore, applying Lemma 2:

$$\Phi_a(r) \equiv \left\{ a \oplus \bigoplus_{i=1}^k \left[ \left( \bigwedge_{j=1}^{i-1} \left( 2^j \bar{a} \right) \right) \wedge \left( 2^i a \right) \wedge \left( 2^i r \right) \right] \right\}$$

$$-\left[\left(\bigwedge_{j=1}^{k} \left(2^{j} \bar{a}\right)\right) \wedge \left(2^{k+1} a\right) \wedge \left(2^{k+1} r\right)\right] \bmod 2^{K}.$$

# Annex 2: Proof of Theorem 2

We begin by the following elementary result:

**Lemma 3** For any z and  $\delta$ , the following identity holds:

$$z + \delta \equiv \overline{\overline{z} - \delta} \bmod 2^K$$

.

*Proof of Lemma 3:* It is easy to see that, for any  $\lambda$ ,

$$\lambda + \bar{\lambda} + 1 \equiv 0 \bmod 2^K.$$

Applying this identity successively with  $\lambda = \bar{z} - \delta$  and  $\lambda = z$ , we obtain:

$$\overline{\bar{z} - \delta} \equiv -(\bar{z} - \delta) - 1 \equiv -((-z - 1) - \delta) - 1 = z + \delta \mod 2^K$$

.

Proof of Theorem 2: We first apply Lemma 3 with z = A and  $\delta = r$ :

$$A + r = \overline{\overline{A} - r}$$

Moreover,

$$\bar{A} = A \oplus (-1) = ((A \oplus r) \oplus (-1)) \oplus r = \overline{A \oplus r} \oplus r.$$

Hence

$$A+r=\overline{(\overline{A\oplus r}\oplus r)-r}=\overline{\varPhi_{\overline{A\oplus r}}(r)}.$$

From Theorem 1 (with  $\overline{A \oplus r}$  instead of x'), we know that:

$$\varPhi_{\overline{A \oplus r}}(r) = \overline{A \oplus r} \oplus \bigoplus_{i=1}^{K-1} \left[ \left( \bigwedge_{j=1}^{i-1} \left( 2^j (A \oplus r) \right) \wedge \left( 2^i (\overline{A \oplus r}) \right) \wedge \left( 2^i r \right) \right],$$

so that

$$A+r=A\oplus r\oplus\bigoplus_{i=1}^{K-1}\Big[\Big(\bigwedge_{j=1}^{i-1}\big(2^{j}(A\oplus r)\Big)\wedge\big(2^{i}A)\big)\wedge\big(2^{i}r\Big)\Big].$$

Let us denote, for any integer  $k \geq 0$ ,

$$u_k = \bigoplus_{i=1}^k \left[ \left( \bigwedge_{j=1}^{i-1} \left( 2^j (A \oplus r) \right) \wedge \left( 2^i A \right) \right) \wedge \left( 2^i r \right) \right].$$

From the definition of  $u_k$ , we have  $u_0 = 0$  and  $A + r = A \oplus r \oplus u_{K-1}$ . Moreover for all  $k \geq 0$ ,

$$u_{k+1} = \bigoplus_{i=1}^{k+1} \left[ \left( \bigwedge_{j=1}^{i-1} \left( 2^j (A \oplus r) \right) \wedge \left( 2^i A \right) \right) \wedge \left( 2^i r \right) \right]$$

$$= 2(A \wedge r) \oplus \bigoplus_{i=2}^{k+1} \left[ \left( \bigwedge_{j=1}^{i-1} \left( 2^j (A \oplus r) \right) \wedge \left( 2^i A \right) \right) \wedge \left( 2^i r \right) \right],$$

so that, if we denote i' = i - 1 and j' = j - 1:

$$u_{k+1} = 2(A \wedge r) \oplus \bigoplus_{i'=1}^{k} \left[ \left( \bigwedge_{j'=0}^{i'-1} \left( 2^{j'+1} (A \oplus r) \right) \wedge \left( 2^{i'+1} A \right) \right) \wedge \left( 2^{i'+1} r \right) \right]$$

$$= 2 \left\{ (A \wedge r) \oplus \bigoplus_{i'=1}^{k} \left[ \left( \bigwedge_{j'=0}^{i'-1} \left( 2^{j'} (A \oplus r) \right) \wedge \left( 2^{i'} A \right) \right) \wedge \left( 2^{i'} r \right) \right] \right\}$$

$$= 2 \left\{ (A \wedge r) \oplus (A \oplus r) \wedge \bigoplus_{i'=1}^{k} \left[ \left( \bigwedge_{j'=1}^{i'-1} \left( 2^{j'} (A \oplus r) \right) \wedge \left( 2^{i'} A \right) \right) \wedge \left( 2^{i'} r \right) \right] \right\}$$

$$= 2 \left[ (A \wedge r) \oplus (A \oplus r) \wedge \oplus (A \oplus r) \wedge u_k \right].$$

# Annex 3: Proof of Theorem 3

Let  $\delta$  be any value in I. We begin by proving that  $\Theta_{\delta}$  is surjective. Let  $y \in I$ . If we denote:

$$\gamma = \bigoplus_{i=0}^{K-1} \left[ \left( \bigwedge_{j=1}^{i} \left( 2^{j-1} \delta \right) \right) \wedge \left( 2^{i} y \right) \right]$$

(conventionally, the empty product  $\bigwedge_{j=1}^{0}$  equals the identity element of the  $\wedge$  operator), we have:

$$\gamma \oplus (2\gamma) \wedge \delta = \gamma \oplus \bigoplus_{i=0}^{K-1} \left[ \left( \bigwedge_{j=0}^{i} \left( 2^{j} \delta \right) \right) \wedge \left( 2^{i+1} y \right) \right],$$

so that, if we denote i' = i + 1 and j' = j + 1:

$$\gamma \oplus (2\gamma) \wedge \delta = \gamma \oplus \bigoplus_{i'=1}^K \left[ \left( \bigwedge_{j'=1}^{i'} \left( 2^{j'-1} \delta \right) \right) \wedge \left( 2^{i'} y \right) \right].$$

From the definition of  $\gamma$ , it is easy to see that:

$$\bigoplus_{i'=1}^{K} \left[ \left( \bigwedge_{i'=1}^{i'} \left( 2^{j'-1} \delta \right) \right) \wedge \left( 2^{i'} y \right) \right] = \gamma \oplus y$$

Therefore:

$$\gamma \oplus (2\gamma) \wedge \delta = y.$$

We have proven that, for any  $y \in I$ , a value  $\gamma \in I$  exists such that  $\Theta_{\delta}(\gamma) = y$ . As a consequence,  $\Theta_{\delta}$  is surjective. Since it maps I onto itself, we deduce that  $\Theta_{\delta}$  is bijective.

# Fast Primitives for Internal Data Scrambling in Tamper Resistant Hardware

Eric Brier<sup>1</sup>, Helena Handschuh<sup>2</sup>, and Christophe Tymen<sup>3</sup>

Gemplus Card International, Card Security Group Parc d'Activités de Gémenos, B.P. 100, 13881 Gémenos, France eric.brier@gemplus.com

<sup>2</sup> Gemplus Card International

34 rue Guynemer, 92447 Issy-les-Moulineaux, France helena.handschuh@gemplus.com

<sup>3</sup> École Normale Supérieure

45 rue d'Ulm, 75230 Paris, France christophe.tymen@gemplus.com

**Abstract.** Although tamper-resistant devices are specifically designed to thwart invasive attacks, they remain vulnerable to micro-probing. Among several possibilities to provide data obfuscations, keyed hardware permutations can provide compact design and easy diversification. We discuss the efficiency of such primitives, and we give several examples of implementations, along with proofs of effectively large key-space.

**Keywords.** Tamper-resistance, Probing attacks, Data scrambling, Keyed permutations, Smart-cards.

### 1 Introduction

Microprobing techniques are invasive attacks consisting in introducing a conductor point into certain parts of a tamper-resistant chip to monitor the electrical signal at this spot[3,1], in order to extract some secret information. A natural means to thwart these attacks consists in encrypting the data stored or exchanged inside the chip. Using classical block-ciphers like DES provides a natural solution, but this method becomes quickly illusory when the concerned data transit through highly time critical processes, like for example the communication between the microprocessor and the RAM. In this case, more hasty techniques must be used to provide very fast processing at the expense of a lower, but acceptable security level. This category of techniques is usually and informally called scrambling, or obfuscation, as opposed to encryption[4].

A popular primitive for scrambling in highly constrained environments consists simply in bit permutations, these permutations being parameterized by a key. As it appears in what follows, such functions result in very compact designs, where only one cycle is needed to process the data. Furthermore, a large number of permutations can be generated, with a one-to-one correspondence with the key space. Ultimately, keyed permutations can be easily used in more complex functions which require some keyed linear components.

More precisely, this paper addresses the problem of designing keyed permutations of compact shape, that generate a large set of permutations when the key runs over the key space, and that offer good properties against chosen plaintext attacks in the context of physical probing. This combinatorial issue is tractable for a small number of bits, but becomes more intricate for realistic values like 16 or 32, which brings intrinsic interest to the results of Section 3. The rest of this paper is organized as follows. Section 2 defines a security model for scrambling functions, and proposes a criterion for the design of keyed permutations. Section 3 is the main part of our paper. Three different constructions for keyed permutations are proposed, along with proofs of some of their properties. Hardware engineers interested in quickly evaluating the practical contribution of this paper can directly jump to Section 4, which contains some numerical data about our new keyed permutations. Some possible applications are also listed. An example of a very fast on-chip data scrambler which integrates keyed permutations is proposed.

# 2 Scrambling Functions and Probing Attacks

# 2.1 Security Model

We consider the context of a smart-card microprocessor, which communicates with the RAM. The memory, and the channel which links it to the microprocessor, are subject to probing attempts. Consequently, to prevent information disclosure, a data word  $(b_0, \ldots, b_{n-1})$  is encrypted with a key K using a scrambling function  $C_K$  before being sent to the memory. The key K may be refreshed each time the card is reset, but might also be regenerated more often, using multiple keys encryption techniques. We assume that the attacker is allowed to play with the microprocessor, which implies that he can send any data he wants to the memory. His goal is to decipher a secret data present in the card, read from the RAM at some time. The difference with a classical chosen plaintext attack on a block-cipher is that the attacker has only a partial knowledge of the ciphertext. Indeed, probing attacks are usually not easy to mount, and in particular, the attacker might rarely probe wherever he wants[3]. Consequently, we restrict the capabilities of the attacker to recovering only *some* of the bits  $(b'_0, \ldots, b'_{n-1}) = C_K(b_0, \ldots, b_{n-1})$ .

# 2.2 A Security Criterion for Linear Functions

For efficiency reasons, it is practical to choose for  $C_K$  a linear function. This choice does not provide any security against full chosen plaintext attacks, but might be sufficient if we assume that the attacker knows very few bits  $b'_i$ . One of the possible strategies of the attacker to decrypt a secret data might be to recover completely K during a preliminary phase when several plaintext messages are sent to the scrambling function. In this context, we can quantify the security provided by  $C_K$  by determining the number of wires that the attacker has to

be able to probe simultaneously to recover the key. In particular, when  $C_K$  is a permutation  $\sigma_K$  of the group  $S_n$  of the permutations of  $\{0,\ldots,n-1\}$ , this question boils down to: what is the minimal number of pairs  $(i,\sigma_K(i))$  the attacker needs to know to recover K entirely? To formalize this condition, we introduce some definitions and notations. If  $\mu$  and  $\sigma$  are two elements of  $S_n$ , we denote by  $\mu\sigma$  the permutation defined by  $i: -\mu(\sigma(i))$ . We also denote by  $\iota$  the permutation such that  $\iota(i)=i$  for all  $i\in\{0,\ldots,n-1\}$ .

An (n,k)-keyed permutation is a map from the set  $\{0,1\}^k$  to  $S_n$ :

$$\sigma: \{0,1\}^k \longrightarrow S_n$$

$$K \longmapsto K$$

The degree of freedom of an (n,k)-keyed permutation is the smallest integer  $m \ge 1$  such that there exists an (m+1)-tuple  $(i_1, \ldots, i_{m+1})$  of pairwise distinct elements of  $\{0, \ldots, n-1\}$ , such that the map

$$\left\{ \sigma_K / K \in \{0, 1\}^k \right\} \longrightarrow \left\{ 0, \dots, n - 1 \right\}^{m+1}$$

$$\sigma_K \longrightarrow \left\{ \sigma_K(i_1), \dots, \sigma_K(i_{m+1}) \right\}$$

is injective. Informally, the degree of freedom is equal to the minimum number of pairs  $(i, \sigma_K(i))$  we have to fix to determine uniquely  $\sigma_K$ . Note that this does not mean that this suffices to determine K, as the map from  $\{0, 1\}^k$  to  $S_n$  might not be injective, but in our context, the secret key is completely recovered as soon as  $\sigma_K$  is known. From a practical standpoint, this definition implies also that we should look for keyed permutations with a degree of freedom as high as possible.

For example, in the strongest case, if  $\sigma$  is surjective in  $S_n$ , then  $\sigma$  has degree of freedom n-1: we need exactly n-1 distinct pairs  $(i,\sigma_K(i))$  to determine completely  $\sigma_K$  (the missing value is inferred from the n-1 others, since  $\sigma_K$  is a bijection). For the weakest case, let  $\mu \neq b$  in  $S_n$ , and consider the keyed permutation  $\sigma_b$  from  $\{0,1\}$  to  $S_n$  such that  $\sigma_0 = \iota$  and  $\sigma_1 = \mu$ . Then  $\sigma$  as degree of freedom one: as  $\mu \neq b$  there exist  $i_1$  such that  $\sigma_b(i_1) \neq b$  iff b=1.

# 3 A Recursive Construction

### 3.1 Outline of the Result

This section explains the construction of three different (n,k)-keyed permutations when n is a power of two. These three constructions can be realized using combinatorial logic, and the corresponding circuits are of depth  $\log_2 n$ . Consequently, they achieve a very compact shape, and very short propagation delay features.

The construction of Section 3.3 generates  $2^{n-1}$  permutations, which are in one-to-one correspondance with the key space. This construction is improved in Section 3.4, where we generate  $n^{n/2}$  permutations. Section 3.5 still improves this result by generating at least  $n^{\alpha n}2^{-\beta n}$  permutations, with  $\alpha = (\log_2 6)/4 \approx 0.65$  and  $\beta = (\log_2 6)/4 - 1/2 \approx 0.15$ . Furthermore, we prove that the last two constructions have degree of freedom at least n/2 - 1.

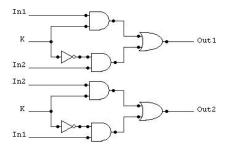

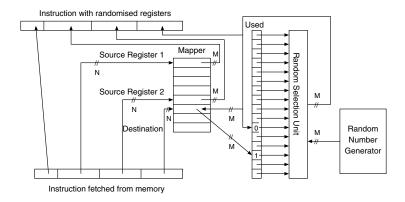

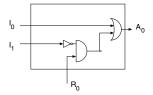

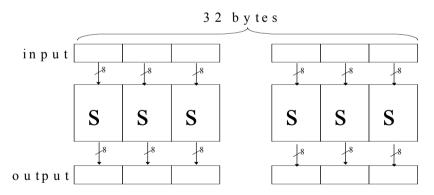

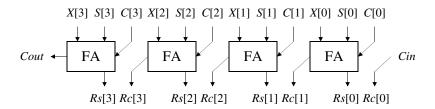

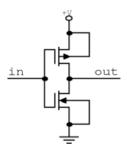

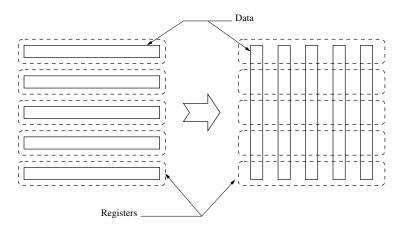

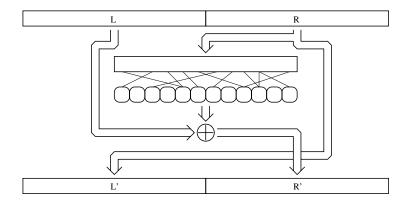

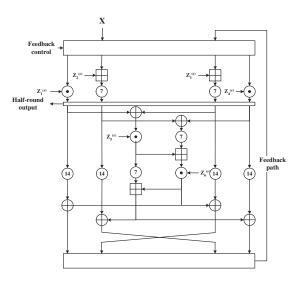

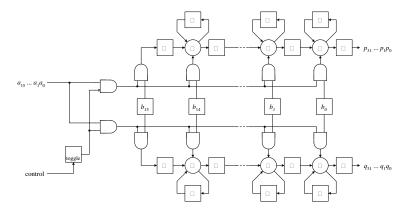

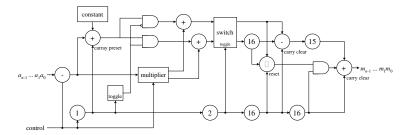

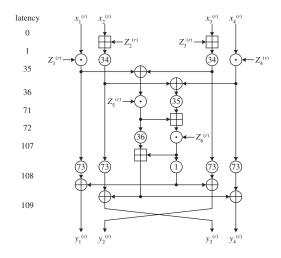

Fig. 1. Hardware realization of a switch

# 3.2 Hardware Representation of Keyed Permutations

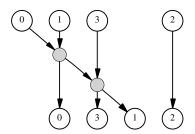

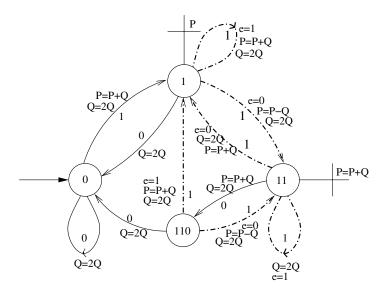

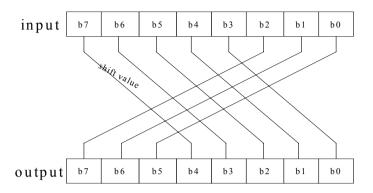

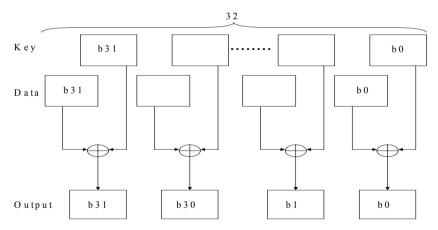

The most natural approach to design hardware permutations is to use the set of the transpositions of  $S_n$ . We recall that a transposition is an element (i, j) of  $S_n$  which exchanges the symbol i with the symbol j. A well-known fact is that every permutation on can be expressed as a product of transpositions. If t is a transposition, a keyed permutation  $b \vdash \neg t^b$  with one bit of key can be realized using two parallel multiplexers. We call such a block a *switch*. A hardware realization of a switch is given in figure 1. Oriented graphs provide a compact representation of switch based circuits. For example, figure 2 represents the keyed permutation  $(b_0, b_1) \vdash \neg (1, 3)^{b_0} (0, 1)^{b_1} \in S_4$ . The grey nodes correspond to the switches, and are commanded by additional key wires, which do not appear on the figure. In the following, the depth of a circuit will refer to the number of stages composing the circuit, this number being related to a switch-based design. Note that the switch-depth is less than or equal to the multiplexer-depth.

**Fig. 2.** Graphical representation of the keyed permutation  $(1,3)^{b_0}(0,1)^{b_1}$

# 3.3 A Group Theoretic Construction

We denote by  $\mathcal{H}_2^n$  a greatest subgroup of  $S_n$  which order is a power of two.  $\mathcal{H}_2^n$  is called a  $Sylow\ 2-subgroup$  of  $S_n$ . In all the following, we will suppose that n is a power of two. In this case,  $\mathcal{H}_2^n$  has order  $2^{n-1}[5]$ . A set of generators of  $\mathcal{H}_2^n$  can be constructed recursively as follows. Consider the set  $\{0,\ldots,n-1\}$ , and

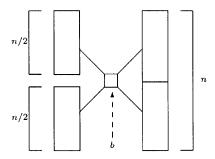

the permutation  $g \in \mathcal{H}_2^n$  which exchanges  $\{0, \ldots, n/2 - 1\}$  with  $\{n/2, \ldots, n - 1\}$  by  $i \leftrightarrow i + n/2$ . Now, we can repeat inductively this procedure by considering the sets  $\{0, \ldots, n/2 - 1\}$  and  $\{n/2, \ldots, n - 1\}$ . We get finally n - 1 elements of  $S_n$  which generate  $\mathcal{H}_2^n$ .

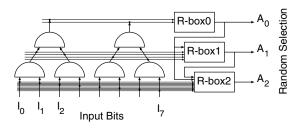

These generators are very easy to implement in hardware, since permuting two sets of k bits can be done using k switches parameterized by the same bit of key. This yields to a  $(n, \log_2 n - 1)$ -keyed permutation, that can be realized using  $(n \log_2 n)/2$  switches. Figure 3 summarizes schematically this recursive construction.

Fig. 3. Recursive contruction based on Sylow 2-subgroups

An interesting property of this design is that the set of generated permutations forms a group. We can take advantage of this fact to increase the number of generated permutations: In our previous construction, we built a hardware design which realized the keyed permutation  $g_K$ , where  $g_K$  takes all the values of  $\mathcal{H}_2^n$  when K runs over the key space. Denote by  $\rho$  a well-chosen permutation, which we implement in hardware, that is, by permuting physically the wires. Then, by reusing the previous construction, we can realize the keyed permutation

$$s_{(K_1,K_2)} = g_{K_1} \circ \rho \circ g_{K_2}$$

,

which should generate more permutations. The question is to determine how many permutations are effectively generated by this method. It is easy to see that no collisions appear (i.e. the number of generated permutations is equal to  $|\mathcal{H}_2^n|^2$ ) iff the following algebraic condition is verified:

$$\rho \mathcal{H}_2^n \rho^{-1} \cap \mathcal{H}_2^n = \{\iota\} . \tag{1}$$

The naive complexity of checking if a given permutation  $\rho$  verifies (1) is equal to  $|\mathcal{H}_2^n| = 2^{n-1}$ . Consequently, our approach fails as soon as say  $n \geq 32$ , since this last verification has to be made 32!/2 times on average before finding a solution. Nevertheless, for n = 32, we may still get a result using the following trick: we define H, the subgroup of  $\mathcal{H}_2^{32}$  which preserves  $\{0, \ldots, 15\}$  and  $\{16, \ldots, 31\}$ . H is isomorphic to  $\mathcal{H}_2^{16} \times \mathcal{H}_2^{16}$ , and has cardinality  $2^{30}$ . Consider the keyed

permutation  $(K_1, K_2) \vdash -h_{K_1}\beta g_{K_2}$ , where  $h_{K_1}$  runs over H,  $g_{K_2}$  runs over  $\mathcal{H}_2^{32}$ , and where  $\beta$  is a fixed permutation. This map is injective iff

$$\beta H \beta^{-1} \cap \mathcal{H}_2^{32} = \{\iota\} . \tag{2}$$

A simple method to find such a  $\beta$  is first to solve (1) for n=16, and then to set  $\beta=(\rho(\cdot),\rho(\cdot-16)+16)$ . This search terminates on average after  $(|S_{16}/\mathcal{H}_2^{16}|\cdot|\mathcal{H}_2^{16}|)^{1/2}\approx 2^{22}$  trials. For instance, the following permutation is a solution of (1) for n=16:

$$\rho = (0, 15, 9, 10, 11, 12, 13, 14)(1, 2, 3)(4, 5, 6, 7, 8)$$

.

The resulting number of generated permutations is equal to  $2^{30} \cdot 2^{31} = 2^{61}$ .

# 3.4 Generalization of the Group-Based Design

Unfortunately, this improvement works only for  $n \leq 32$ . Furthermore, we generate only  $2^{61}$  permutations, among the  $32! \approx 2^{118}$  elements of  $S_{32}$ . Nevertheless, as we will see, a slight modification of the set of generators leads to generating a much larger subset of  $S_n$ . The price to pay for this improvement is to lose the group property, but this has no impact for our application. As before, the solution is built recursively by induction on  $\log_2 n$ , so that at each step of the induction, we add a new stage to the corresponding circuit.

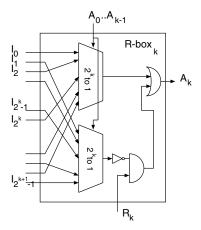

**Theorem 1.** If n is a power of two, then there exists a circuit of depth  $\log_2 n$  involving  $(n \log_2 n)/2$  switches, which realizes a  $(n, (n \log_2 n)/2)$ -keyed permutation  $\delta$ . Furthermore, the number of distinct generated permutations is equal to the number of keys, that is  $n^{n/2}$ .

*Proof.* We proceed by induction. Let  $\sigma$  be a  $(n/2, ((n/2)\log_2(n/2))/2)$ -keyed permutation with the properties stated in the theorem. For convenience, we set  $k = ((n/2)\log_2(n/2))/2$ . First, we defined the (n, 2k)-keyed permutation  $\mu$  as

$$\mu_{(K_1, K_2)}(i) = \begin{cases} \sigma_{K_1}(i) & \text{if } 0 \le i < n/2\\ \sigma_{K_2}(i - n/2) + n/2 & \text{if } n/2 \le i < n \end{cases},$$

(3)

where  $K_1, K_2 \in \{0,1\}^k$ . Let set k' = 2k + n/2, and define the (n, k')-keyed permutation  $\delta$  by

$$\delta_{(K_1,K_2,E)} = \nu_E \circ \mu_{(K_1,K_2)}$$

,

where

$$\nu_E = \prod_{j=0}^{n/2-1} (j, j+n/2)^{e_j} ,$$

and  $E = (e_0, \dots, e_{n/2-1}) \in \{0, 1\}^{n/2}$ . First,  $k' = 2k + n/2 = n(\log_2 n - 1)/2 + n/2 = (n \log_2 n)/2$ , which corresponds to what we expect. Furthermore, the number of switches used for realizing  $\delta$  is equal to 2k + n/2 = k'. It remains to prove that  $\delta$  is injective. This comes from the fact that for all  $0 \le i < n/2$ ,

$\delta_{(K_1,K_2,E)}^{-1}(i) < n/2$  iff  $e_i = 0$ . Consequently, we can uniquely recover E from  $\delta_{(K_1,K_2,E)}$ . As  $\mu$  is injective, we can also recover uniquely  $K_1$  and  $K_2$  from  $\mu_{(K_1,K_2)} = \nu_E^{-1} \circ \delta_{(K_1,K_2,E)}$ , which concludes the proof.

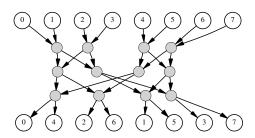

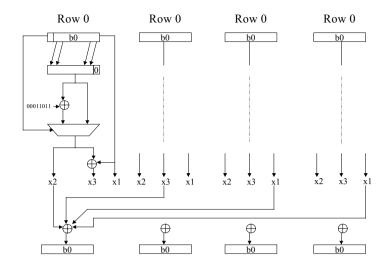

Figure 4 represents an example of this construction for the case n = 8.

**Fig. 4.** Representation of  $\delta$  for n=8

As motivated in section 2.2, we want to check that  $\delta$  has high enough degree of freedom. This is guaranteed by the following result :

**Theorem 2.** The degree of freedom  $d_{\delta}$  of the keyed permutation  $\delta$  of theorem 1 verifies

$$d_{\delta} \geq n/2 - 1$$

.

*Proof.* We proceed by induction on n. When n=2, the theorem is true, as in order to guess the state of the switch, we have to know at least one pair  $(i, \delta_K(j))$ . Suppose that the theorem is true at step n/2. Recall that with the notations of theorem 1,  $\delta$  is given by the recursion formula

$$\delta_{K=(K_1,K_2,E)} = \nu_E \circ \mu_{(K_1,K_2)}$$

,

where  $\mu$  is defined from the (n/2,k)-keyed permutation  $\sigma$  following (3). The induction formula implies that  $\sigma$  has degree of freedom n/4-1. We set r=n/2-1, and we choose an r-tuple  $(i_1,\ldots,i_r)$  of pairwise distinct elements of  $\{0,\ldots,n-1\}$ , a key  $K=(K_1,K_2,E)$ , and we set  $j_l=\delta_K(i_l)$ . Consider the set  $I_1=\{l/\nu_E^{-1}(j_l)< n/2\}$ , and  $I_2=\{l/\nu_E^{-1}(j_l)\geq n/2\}$ . As  $|I_1|+|I_2|=n/2-1$ , one of the two sets (for example  $I_1$ ) has strictly less than n/4 elements:  $|I_1|\leq n/4-1$ . Furthermore, as  $\mu$  preserves  $\{0,\ldots,n/2-1\}$  and  $\{n/2,\ldots,n-1\}$ , for all  $l\in I_1$ ,  $i_l< n/2$ . Consequently, there exists  $K_1'$  /  $K_1$  such that

$$\forall l \in I_1, \ \sigma_{K_1}(i_l) = \sigma_{K'_1}(i_l) \ .$$

This implies that

$$\delta_{(K_1,K_2,E)}(i_1,\ldots,i_r) = \delta_{(K'_1,K_2,E)}(i_1,\ldots,i_r)$$

.

This proves that  $\delta$  has degree of freedom greater than n/2-1.

# 3.5 Further Improvements

We may still try to improve the previous construction by modifying it so that we could generate a larger set of permutations. We always consider the keyed permutation  $\delta$  as defined above, with the recursion formula

$$\delta_{K=(K_1,K_2,E)} = \nu_E \circ \mu_{(K_1,K_2)}$$

.

Define the vector  $\epsilon = (\epsilon_0, \dots, \epsilon_{n-1})$  as  $\epsilon_i = \mathbf{1}\{\delta_K^{-1}(i) < n/2\}$ , where  $\mathbf{1}\{P\}$  is equal to one when the predicate P is true, and to zero otherwise. As underlined in the proof of theorem 1, there is a one-to-one correspondence between the set of all the keys E and the set of all the n/2-tuples  $(\epsilon_0, \dots, \epsilon_{n/2-1})$ . This is because  $\mu$  preserves the segments i < n/2 and  $i \ge n/2$ . This means that  $\epsilon$  contains twice too much information. Consequently, our idea is to group the transpositions (j, j + n/2) of  $\mu$  two by two, and to compose them with a cycle of the four concerned elements, so that we could still invert our map thanks to the associated 4-tuple of bits  $\epsilon_i$ .

Consider first the set  $\{0, 1, 2, 3\}$ , and the map

$$g: (b_0, b_1, b_2) \in \{0, 1\}^3 + - (0, 2, 1, 3)^{b_0} (0, 2)^{b_1} (1, 3)^{b_2}$$

.

We consider also the map defined by

$$h(b_0, b_1, b_2) = (\mathbf{1}\{g(b_0, b_1, b_2)^{-1}(i) < 2\})_{0 \le i \le 3}$$

.

The truth table of h is given below:

| $(b_0, b_1, b_2)$ | $h(b_0, b_1, b_2)$ |

|-------------------|--------------------|

| (0,0,0)           | (1,1,0,0)          |

| (0, 0, 1)         | (1,0,0,1)          |

| (0, 1, 0)         | (0,1,1,0)          |

| (0, 1, 1)         | (0,0,1,1)          |

| (1, 0, 0)         | (0,0,1,1)          |

| (1, 0, 1)         | (1,0,1,0)          |

| (1, 1, 0)         | (0,1,0,1)          |

| (1, 1, 1)         | (1,1,0,0)          |

As it can be seen,  $h(\{0,1\}^3)$  has cardinality six.

Now, group the points of  $\{0, \ldots, n-1\}$  four by four (when  $n \ge 4$ ):

$$A_0 = (0, 1, n/2, n/2 + 1),$$

$A_1 = (2, 3, n/2 + 2, n/2 + 3),$

$\vdots$

$A_{n/4-1} = (n/2 - 2, n/2 - 1, n - 2, n - 1).$

Finally, form the cycles  $c_0, \ldots, c_{n/4-1}$ , with support respectively equal to the  $A_i$ , obtained from the cycle (0, 2, 1, 3) by applying for each  $0 \le i < n/4$  the substitutions

$$0 + -i$$

,  $1 + -i + 1$ ,  $2 + -n/2 + i$ ,  $3 + -n/2 + i + 1$ .

24

We are now ready to build recursively a keyed permutation  $\chi$ , with the same method as in the proof of theorem 1. Following analogous notations, we define  $\chi_{(K_1,K_2,E,F)}$  inductively as

$$\chi_{(K_1, K_2, E, F)} = \xi_F \circ \nu_E \circ \mu_{(K_1, K_2)} , \qquad (4)$$

where

$$\xi_F = \prod_{j=0}^{n/4-1} c_j^{f_j} ,$$

with  $F = (f_0, \dots, f_{n/4-1}) \in \{0, 1\}^{n/4}$ .

**Theorem 3.**  $\chi$  is a (n,k)-keyed permutation, where  $k = \frac{3}{4}n \log_2 n$ .  $\chi$  can be realized using k switches, and has degree of freedom at least n/2-1. Furthermore,  $\chi$  generates at least  $a_n$  distinct permutations, where  $a_n$  verifies the recursion formula

$$\begin{cases} a_n = 6^{n/4} a_{n/2}^2 & \text{if } n \ge 4 \\ a_2 = 2 & . \end{cases}$$

*Proof.* We prove the recursion formula, the verification of the other points being straightforward. Suppose that we have constructed an (n/2, k)-keyed permutation  $\sigma$  that verifies our statements. We denoted by  $\mathcal{E}$  the largest set of the keys such that  $\sigma$  restricted to  $\mathcal{E}$  is injective. Referring to the recursive construction of  $\chi$  of equation (4), it is clear that  $\mu$  restricted to  $\mathcal{E} \times \mathcal{E}$  is injective: this is a direct consequence of definition (3) of  $\mu$ . Consider for each  $0 \le i < n/4$  the 3-tuples  $U_i = (e_{2i}, e_{2i+1}, f_i)$ , and the set

$$\mathcal{A} = \left\{ (0,0,0), (0,0,1), (0,1,0), (0,1,1), (1,0,1), (1,1,0) \right\} \ .$$

Using the truth table of h, we see that h restricted to  $\mathcal{A}$  is injective. Consider the set  $\mathcal{F}$  of the keys defined by  $\mathcal{F} = \{(E, F)/\forall i \ U_i \in \mathcal{A}\}$ . It is clear that

$$|\mathcal{F}| = |\mathcal{A}|^{n/4} = 6^{n/4}$$

(5)

Now, since  $\mu_{(K_1,K_2)}$  preserves the sets  $\{0,\ldots,n/2-1\}$  and  $\{n/2,\ldots,n-1\}$ , we have that

$$\chi_K^{-1}(i) < n/2 \Longleftrightarrow (\xi_F \circ \nu_E)^{-1}(i) < n/2$$

.

This implies that  $\chi$  restricted to  $\mathcal{E} \times \mathcal{E} \times \mathcal{F}$  is injective. Using equality (5) and the fact that  $|\mathcal{E}| \geq a_{n/2}$ , this proves the theorem.

It is easy to check by induction that  $\log_2 a_n > (n \log_2 n)/2$ , which means that  $\chi$  generates effectively more permutations than  $\delta$ . The explicit expression of  $a_n$  announced in section 3.1 results from the fact that the sequence  $(\log_2 a_n)/n$  is in arithmetic progression.

Contrary to  $\delta$ , the distribution of the permutations generated by  $\chi_K$ , when K is chosen uniformly, is not uniform. We leave open the question of determining exactly this distribution. Anyway, it is easy to reduce the key space so that the

restriction of  $\chi$  becomes injective. For that, it suffices to restrict the keys (E, F) to the set  $\mathcal{F}$  defined in the proof above, and to proceed by induction. We leave open the question of the exact distribution of the generated permutations.

The practical realization of  $\chi$  implies to design in hardware a keyed permutation with a cycle of length four, like  $(0,1,2,3)^b, b \in \{0,1\}$ . This can be easily done in one stage using four multiplexers

Figure 5 shows a realization of  $\chi$  for the case n = 8. The nodes with 8 edges represent the cycle (0, 2, 1, 3) involved in the construction of  $\chi$ .

**Fig. 5.** Representation of  $\chi$  for n=8

# 4 Practical Examples and Applications

# 4.1 Numerical Examples

Table 1 shows the characteristics of the two keyed permutations  $\delta$  and  $\chi$  for various values of n=8,16,32,64. The number of multiplexers needed for their construction is denoted by  $N_{\rm mux}$ , and the number of distinct generated permutations is denoted by  $N_{\rm perm}$ .

|                              | δ  | χ  | $\delta$ | χ   | $\delta$ | χ   | $\delta$ | χ   |

|------------------------------|----|----|----------|-----|----------|-----|----------|-----|

| $\overline{n}$               | 8  | 3  | -        | 16  | 3        | 2   | 6        | 4   |

| $N_{ m mux}$                 | 32 | 40 | 88       | 112 | 224      | 288 | 544      | 704 |

| Depth                        | 3  | 6  | 4        | 8   | 5        | 10  | 6        | 12  |

| Key size                     | 12 | 16 | 32       | 44  | 80       | 112 | 192      | 272 |

| ${[\log_2 N_{\text{perm}}]}$ | 12 | 14 | 32       | 39  | 80       | 99  | 192      | 239 |

|                              | 1  | 5  | 4        | 14  | 10       | 18  | 29       | 96  |

**Table 1.** Characteristics of  $\delta$  and  $\chi$  for various values of n

An important fact is the very small number of stages needed to implement  $\delta$  and  $\chi$ . For example, for n=32, the design has only five levels of gates. This property makes these functions particularly suitable for data scrambling in critical pathes. Non exhaustive applications are: scrambling of the bus between the microprocessor and the memory, scrambling of the RAM, or scrambling of the bus between the CPU and the cryptoprocessor.

#### 4.2 Protecting the Secrecy of the Design

These functions can also easily be diversified, and thus provide a customizable design, so that the final scrambling function can remain secret. Recall that  $\delta$  is built recursively from the equation

$$\delta_{(K_1,K_2,E)} = \nu_E \circ \mu_{(K_1,K_2)}$$

.

This definition would correspond to the "normal form" of our construction. Derivated forms can be obtained as follows: at each step of the induction, we choose two permutations  $\alpha_1, \alpha_2$ , acting respectively on  $\{0, \ldots, n/2 - 1\}$  and on  $\{n/2, \ldots, n-1\}$ , and we implement these permutations in hardware, that is, we permute physically the wires of the circuit. Here,  $\alpha_1$  and  $\alpha_2$  are supposed to be kept secret. With the same material, we can now build  $\delta$  using the modified equation

$$\delta_{(K_1,K_2,E)} = \nu_E \circ \alpha_1 \circ \alpha_2 \circ \mu_{(K_1,K_2)} .$$

It is not difficult to see that we generate *mutatis mutandis* the same number of permutations as before, and that the resulting keyed permutation has the same degree of freedom. It suffices for this to rewrite the proofs of theorems 1 and 2. The same construction can be applied to  $\chi$ , with the same consequences.

#### 4.3 Non-linear Data Scrambling Using Keyed Permutations

The primitives that we have just described can easily be incorporated into more complex non-linear data scrambling functions. One major advantage of the proposed constructions is the large size of the key-space and of the resulting function space. Besides, the very compact shape of the resulting circuits allows to use them several times in more complex functions.

Following Shannon's basic confusion-diffusion paradigm, these keyed permutations can be used in alternating layers with small, say 4 bit to 4 bit substitution boxes (S-boxes). Clearly, such constructions cannot achieve the same security level as classical block ciphers do: following Shamir's security analysis [6], a five layer SASAS construction using alternating layers of S-boxes and affine functions (of which permutations are a special case) can be broken using approximately 2<sup>16</sup> chosen plaintexts for 128 bit blocks and 8-bit to 8-bit Sboxes.

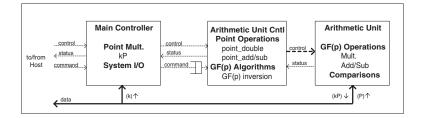

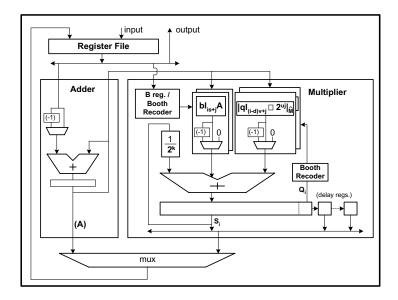

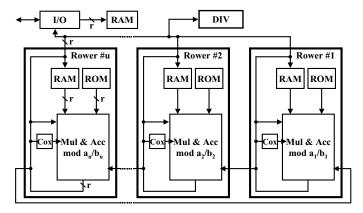

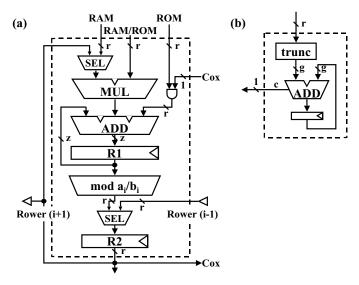

However, this kind of construction still yields a sub-exponential security bound instead of a linear security bound in terms of chosen plaintext attacks. As the attacker has quite limited resources in the probing setting anyhow, bearing in mind that she is not able to probe more than a handful of wires simultaneously using the same session scrambling key, a limited number of layers of additional key-dependent S-boxes will sufficiently increase the difficulty of unscrambling the memory and bus contents in the context of tamper-resistant objects such as smart-cards.